| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

Поддержка

Статьи появляются по мере возникновения Ваших вопросов,

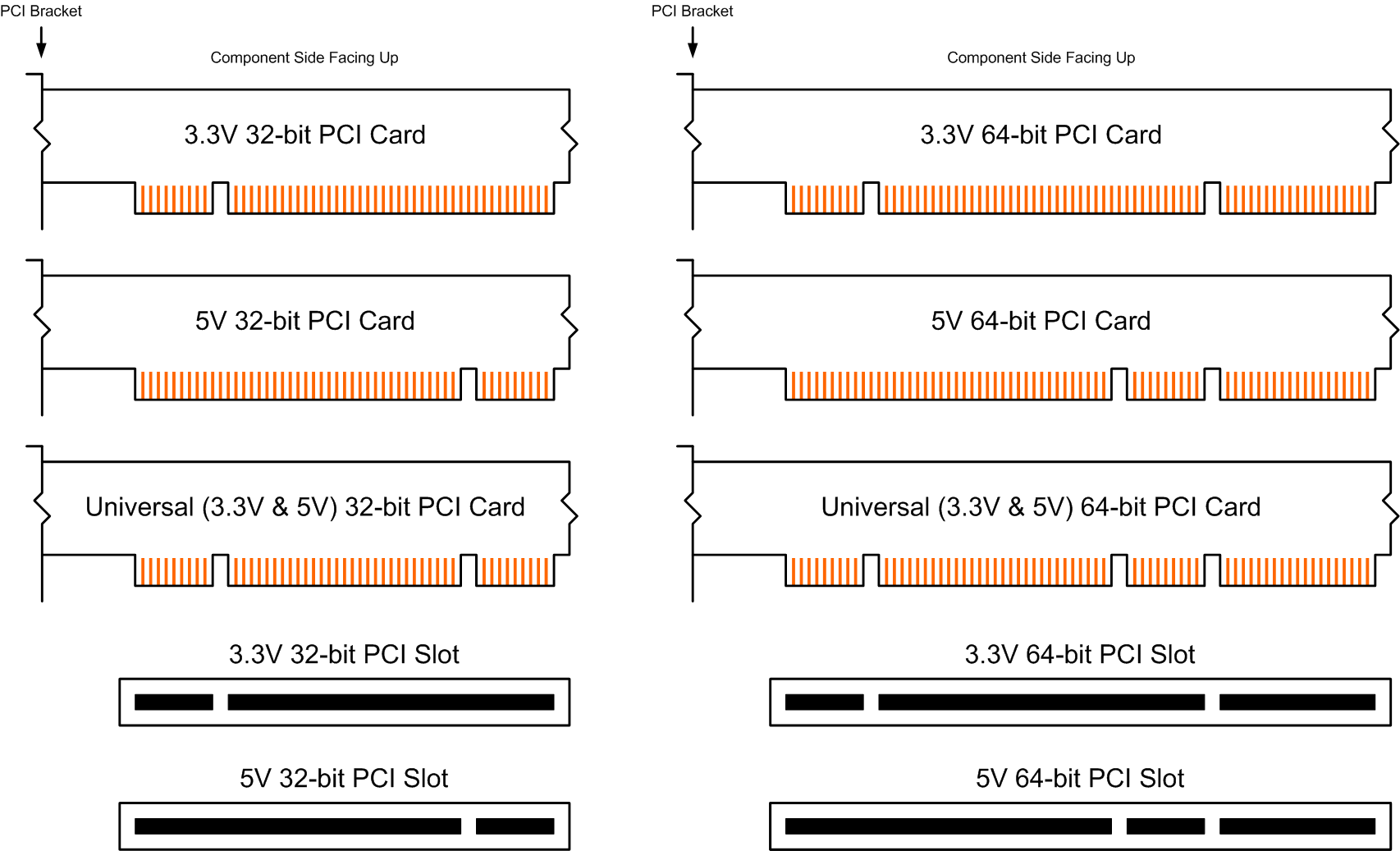

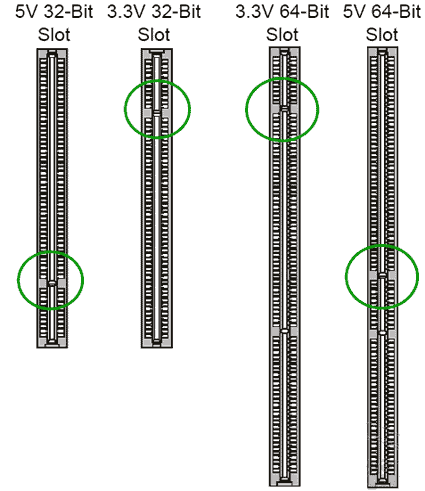

заданных в отделе технической поддержки или в письме на адрес: infodars@yandex.ru К оглавлениюPCI вер. 2.0-3.0 шина 32/64 питание 3.3-5VPeripheral Component Interconnect - Внешний соединитель перифирийных компонент.

Синхронная шина для расширения возможности EISA. Продолжение развития VLB. Разрядность 32 или 64 бита. Располагается сегментами, по 4 разъема в сегменте. Сегменты соединяются посредством специальных устройств - Bridge (мост). Разъем имеет 124 контакта. Питание двух типов - 5.0В и 3.3В. Пропускная способность от 132МБ/с до 528МБ/с. Поддержка Bus Master, автоконфигурации.

PCI Universal Card 32/64 bit

----------------------------------------------------------------

| PCI Component Side (side B) |

| |

| |

| optional |

| ____ mandatory 32-bit pins 64-bit pins _____|

|___| |||||||--|||||||||||||||||--|||||||--||||||||||||||

^ ^ ^ ^ ^ ^ ^ ^

b01 b11 b14 b49 b52 b62 b63 b94

PCI 5V Card 32/64 bit | optional | | ____ mandatory 32-bit pins 64-bit pins _____| |___| ||||||||||||||||||||||||||--|||||||--|||||||||||||| PCI 3.3V Card 32/64 bit | optional | | ____ mandatory 32-bit pins 64-bit pins _____| |___| |||||||--||||||||||||||||||||||||||--||||||||||||||

Задняя панель компьютера

:------:------:

-12V |- B1 A1 -| Test Reset

Test Clock |- B2 A2 -| +12V

Ground |- B3 A3 -| Test Mode Select

Test Data Output |- B4 A4 -| Test Data Input

+5V |- B5 A5 -| +5V

+5V |- B6 A6 -| Interrupt A

Interrupt B |- B7 A7 -| Interrupt C

Interrupt D |- B8 A8 -| +5V

PRSNT1# |- B9 A9 -| Reserved

Reserved |- B10 A10 -| +V I/O

PRSNT2# |- B11 A11 -| Reserved

:------:------:

:------:------:

Reserved |- B14 A14 -| Reserved

Ground |- B15 A15 -| Reset

Clock |- B16 A16 -| +V I/O

Ground |- B17 A17 -| Grant

Request |- B18 A18 -| Ground

+V I/O |- B19 A19 -| Reserved

Address 31 |- B20 A20 -| Address 30

Address 29 |- B21 A21 -| +3.3V

Ground |- B22 A22 -| Address 28

Address 27 |- B23 A23 -| Address 26

Address 25 |- B24 A24 -| Ground

+3.3V |- B25 A25 -| Address 24

C/BE 3 |- B26 A26 -| Init Device Select

Address 23 |- B27 A27 -| +3.3V

Ground |- B28 A28 -| Address 22

Address 21 |- B29 A29 -| Address 20

Address 19 |- B30 A30 -| Ground

+3.3V |- B31 A31 -| Address 18

Address 17 |- B32 A32 -| Address 16

C/BE 2 |- B33 A33 -| +3.3V

Ground |- B34 A34 -| Cycle Frame

Initiator Ready |- B35 A35 -| Ground

+3.3V |- B36 A36 -| Target Ready

Device Select |- B37 A37 -| Ground

Ground |- B38 A38 -| Stop

Lock |- B39 A39 -| +3.3V

Parity Error |- B40 A40 -| Snoop Done

+3.3V |- B41 A41 -| Snoop Backoff

System Error |- B42 A42 -| Ground

+3.3V |- B43 A43 -| PAR

C/BE 1 |- B44 A44 -| Address 15

Address 14 |- B45 A45 -| +3.3V

M66EN/Ground |- B46 A46 -| Address 13

Address 12 |- B47 A47 -| Address 11

Address 10 |- B48 A48 -| Ground

Ground |- B49 A49 -| Address 9

:------:------:

:------:------:

Address 8 |- B52 A52 -| C/BE 0

Address 7 |- B53 A53 -| +3.3V

+3.3V |- B54 A54 -| Address 6

Address 5 |- B55 A55 -| Address 4

Address 3 |- B56 A56 -| Ground

Ground |- B57 A57 -| Address 2

Address 1 |- B58 A58 -| Address 0

+5 I/O |- B59 A59 -| +V I/O

Acknowledge 64-bit |- B60 A60 -| Request 64-bit

+5V |- B61 A61 -| +5V

+5V |- B62 A62 -| +5V

:------:------:

:------:------:

Reserved |- B63 A63 -| Ground

Ground |- B64 A64 -| C/BE 7

C/BE 6 |- B65 A65 -| C/BE 5

C/BE 4 |- B66 A66 -| +V I/O

Ground |- B67 A67 -| Parity 64-bit

Address 63 |- B68 A68 -| Address 62

Address 61|- B69 A69 -| Ground

+V I/O |- B70 A70 -| Address 60

Address 59 |- B71 A71 -| Address 58

Address 57 |- B72 A72 -| Ground

Ground |- B73 A73 -| Address 56

Address 55 |- B74 A74 -| Address 54

Address 53 |- B75 A75 -| +V I/O

Ground |- B76 A76 -| Address 52

Address 51 |- B77 A77 -| Address 50

Address 49 |- B78 A78 -| Ground

+V I/O |- B79 A79 -| Address 48

Address 47 |- B80 A80 -| Address 46

Address 45 |- B81 A81 -| Ground

Ground |- B82 A82 -| Address 44

Address 43 |- B83 A83 -| Address 42

Address 41 |- B84 A84 -| +V I/O

Ground |- B85 A85 -| Address 40

Address 39 |- B86 A86 -| Address 38

Address 37 |- B87 A87 -| Ground

+V I/O |- B88 A88 -| Address 36

Address 35 |- B89 A89 -| Address 34

Address 33 |- B90 A90 -| Ground

Ground |- B91 A91 -| Address 32

Reserved |- B92 A92 -| Reserved

Reserved |- B93 A93 -| Ground

Ground |- B94 A94 -| Reserved

:------:------:

PCI временные диаграммы:

___ ___ ___ ___ ___ ___

CLK ___| |___| |___| |___| |___| |___| |___

_______ _________

FRAME |_________________________________|

______ _______ ______ ______ ______

AD -------<______><_______><______><______><______>---

Address Data1 Data2 Data3 Data4

______ _______________________________

C/BE -------<______><_______________________________>---

Command Byte Enable Signals

____________ ___

IRDY |_________________________________|

_____________ ___

TRDY |________________________________|

______________ ___

DEVSEL |_______________________________|

PCI циклы передачи, 4 фазы данных, без ожидания. Данные передаются по переднему фронту CLK

[1] [2] [3]

___ ___ ___ ___ ___ ___ ___ ___

CLK ___| |___| |___| |___| |___| |___| |___| |___| |__

_______ _________

FRAME |________________________________________________|

A B C

______ ______________ ______ _____________

AD -------<______>---------<______________><______><_____________>---

Address Data1 Data2 Data3

______ ______________________________________________

C/BE -------<______><______________________________________________>---

Command Byte Enable Signals

Wait

____________ _____ ___

IRDY |__________________________________| |_______|

Wait Wait

______________________ ______ ___

TRDY |_______| |_______________________|

______________ ___

DEVSEL |______________________________________________|

PCI циклы передачи с ожиданием. Данные передаются по переднему фронту CLK в точках, обозначенных A, B и C. Шина PCI рассматривает все передачи как пакетную операцию. Каждый цикл начинается с фазы передачи адреса, за которой следуют одна или несколько фаз передачи данных. Фазы передачи данных могут повторяться неопределенно долго, но ограничены таймером, который определяет максимальное время, в течение которого устройство PCI может управлять шиной. Этот таймер устанавливается ЦП как часть пространства конфигурации. Каждое устройство имеет свой собственный таймер (см. Таймер задержки в конфигурационном пространстве). Те же строки используются для адреса и данных. Командные строки также используются для строк включения байтов. Это делается для уменьшения общего количества контактов на разъеме PCI. Командные строки (C / BE3 - C / BE0) указывают тип передачи по шине во время фазы адреса.

|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||